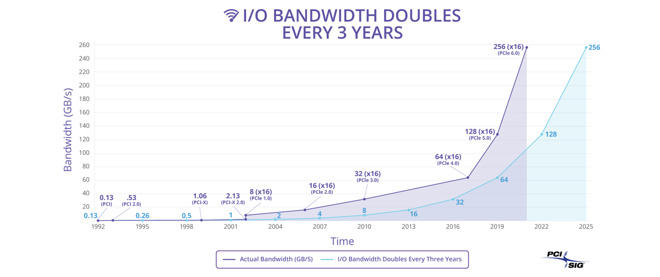

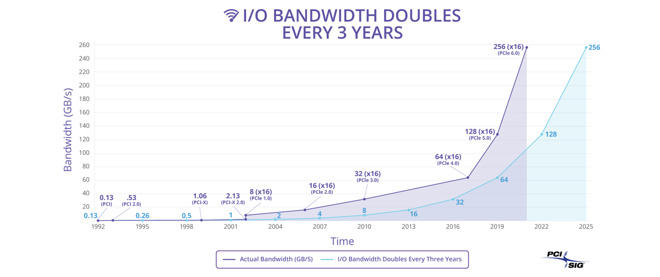

PCIe 6.0 will double the bandwidth of PCIe 5.0 to 256GB/s in 2021

Just a few months after standards for PCIe 5.0 were ratified, PCI-SIG has announced the specification for PCIe 6.0, a connection that will double the effective bandwidth from PCIe 5.0 to a maximum of 256 gigabytes per second.

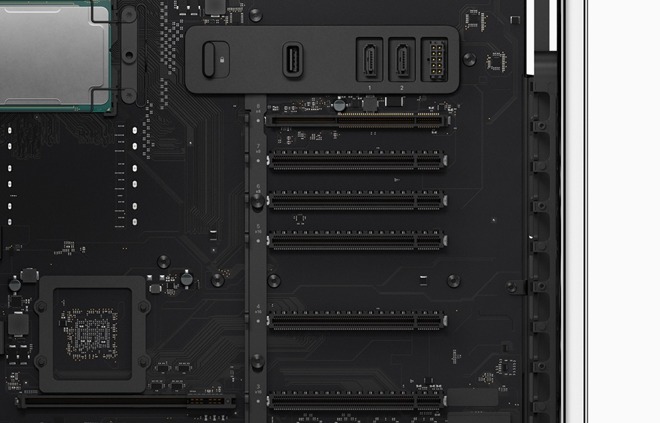

The PCI 3.0 ports included in the modular Mac Pro

The new standard is described as performing 64 "gigatransfers" per second, twice that of PCIe 5.0, four times that of PCIe 4.0, and eight times the capabilities of the commonly-used PCIe 3.0. The high 256 gigabytes per second of bandwidth also follows a similar multiplier, being eight times better than PCIe 3.0's 32 gigabytes per second.

The same multiplier over earlier versions also applies to the frequency, with PCIe 6.0 functioning at 64GHz. For reference, PCIe 4.0 and PCIe 3.0 operate at 16GHz and 8 GHz respectively.

To enable these higher speeds, PCI-SIG is also implementing PAM4 (Pulse Amplitude Modulation) signaling in PCIe 6.0 rather than the NRZ encoding scheme. Commonly used in networking, it uses low latency Forward Error Correction (FEC) with additional mechanisms to boost bandwidth efficiency.

Backwards compatibility with all previous PCIe generations is also pledged, as well as continuing to have a maximum lane count of 16, keeping it in line with other versions.

While the standard offers considerable bandwidth boosts over the existing PCIe 3.0 and slowly-arriving PCIe 4.0, there will still be quite a wait for it to become usable. Current expectations are for the specification to be published in 2021, with the first devices using it potentially arriving in 2022.

At the moment PCIe 3.0 is the prevalent technology, with PCI 4.0 hardware slowly arriving on the market. The ratification of PCIe 5.0 in January could lead to hardware using the standard arriving later in 2019, effectively outdating PCI 4.0 before it can become widely used.

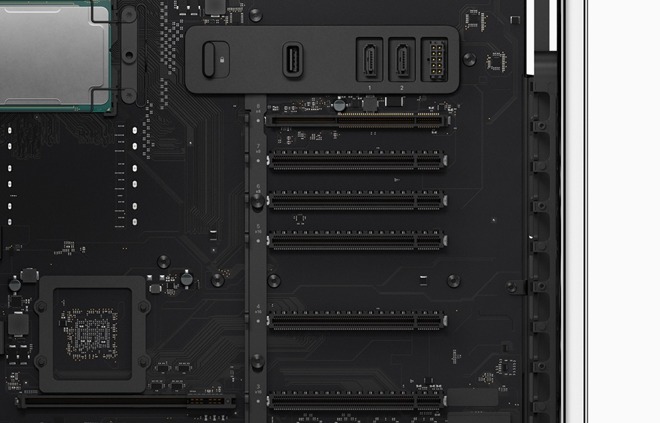

The incoming PCIe 5.0 and the future PCIe 6.0 may be why Apple elected to stick with PCIe 3.0 in the new modular Mac Pro instead of using PCIe 4.0. As Apple is an early backer of technologies like USB, FireWire, and Thunderbolt, it is likely to use the standard in a future product, though the first signs of such usage may be years away, even beyond 2022.

The PCI 3.0 ports included in the modular Mac Pro

The new standard is described as performing 64 "gigatransfers" per second, twice that of PCIe 5.0, four times that of PCIe 4.0, and eight times the capabilities of the commonly-used PCIe 3.0. The high 256 gigabytes per second of bandwidth also follows a similar multiplier, being eight times better than PCIe 3.0's 32 gigabytes per second.

The same multiplier over earlier versions also applies to the frequency, with PCIe 6.0 functioning at 64GHz. For reference, PCIe 4.0 and PCIe 3.0 operate at 16GHz and 8 GHz respectively.

To enable these higher speeds, PCI-SIG is also implementing PAM4 (Pulse Amplitude Modulation) signaling in PCIe 6.0 rather than the NRZ encoding scheme. Commonly used in networking, it uses low latency Forward Error Correction (FEC) with additional mechanisms to boost bandwidth efficiency.

Backwards compatibility with all previous PCIe generations is also pledged, as well as continuing to have a maximum lane count of 16, keeping it in line with other versions.

While the standard offers considerable bandwidth boosts over the existing PCIe 3.0 and slowly-arriving PCIe 4.0, there will still be quite a wait for it to become usable. Current expectations are for the specification to be published in 2021, with the first devices using it potentially arriving in 2022.

At the moment PCIe 3.0 is the prevalent technology, with PCI 4.0 hardware slowly arriving on the market. The ratification of PCIe 5.0 in January could lead to hardware using the standard arriving later in 2019, effectively outdating PCI 4.0 before it can become widely used.

The incoming PCIe 5.0 and the future PCIe 6.0 may be why Apple elected to stick with PCIe 3.0 in the new modular Mac Pro instead of using PCIe 4.0. As Apple is an early backer of technologies like USB, FireWire, and Thunderbolt, it is likely to use the standard in a future product, though the first signs of such usage may be years away, even beyond 2022.

Comments

PCIe3 was introduced in 2010 and has been the industry standard for the past seven years. PCIe4 was adopted by nobody but AMD and while it does double the bandwidth, it will never gain traction now because PCIe5, which is more likely to start appearing late next year and should carry us through most of the next decade, doubles things again. I expect PCIe5 will enjoy something just slightly less than the lifespan of PCIe3 (which is still on nearly every machine with slots being sold to this day, and will be for another year or two minimum).

It is very likely that Intel was aware of the PCIe5 spec being close to ratification and opted to wait — sensibly IMO — for consumer demand to make it the new standard, rather than take the “fast obsolescence” path AMD chose. The market that actually needs PCIe5 (which, reminder, isn’t “out there” in the market yet either) is niche compared to the mainstream of computer users.

As for next year’s Mac Pro buyers, I don’t think they’ll be complaining for a good few years to come, and by that time a Mac Pro with PCIe5 support is likely to be out or about to come out.

Source: [wccftech]

Intel Xeon Cascade Lake does not support PCIe Gen4, and even the next 14nm++ generation, Cooper Lake (2020), also does not, at least not in samples currently shipping. Note that Cooper Lake has a new socket (LGA 4189) and platform, Whitley, which it shares with the first 10nm+ generation, Ice Lake (2020), which will support PCIe Gen4. The new socket and platform support eight channels of DDR4 memory.

Both of the above currently exist -- we can assume Apple already knows what will happen with Xeon-W.

After that is 10nm++ Sapphire Rapids in 2021 with PCIe Gen5 and DDR5 support, but that has another new platform, Eagle Stream.

So it's very possible that Apple will skip PCIe Gen4 -- it may depend on what Intel does with Xeon-W in relation to the above dual (both 14nm and 10nm) approach to Xeon-Scalable (a.k.a. Xeon-SP). If only Cooper Lake gets Xeon-W and it uses the new socket/platform, then Apple might choose to skip from PCIe Gen3 directly to PCIe Gen5 in late 2021 or 2022.

Given Intel's troubles with the 10nm process, it seems unlikely that Ice Lake would be used for Xeon-W. But maybe they've solved the yield problems?

here is a pretty thorough article on this from Anandtech:

https://www.anandtech.com/show/14559/pci-express-bandwidth-to-be-doubled-again-pcie-60-announced-spec-to-land-in-2021

read the very last paragraph.

Looking back, if we'd stopped upping the specs every few years things would be a lot worse currently. Yea all these crazy bandwidth numbers seem insanely useless, but so did needing gobs of RAM years ago and look where we are now.

If you build it, they will come (and find a use for it).