A20 chip developments could mean more iPhone variants in 2026

A change in the way TSMC makes chips for Apple could mean a lot more variation in performance for the iPhone 18 models, by Apple switching combinations of CPU, GPU, and Neural Engine.

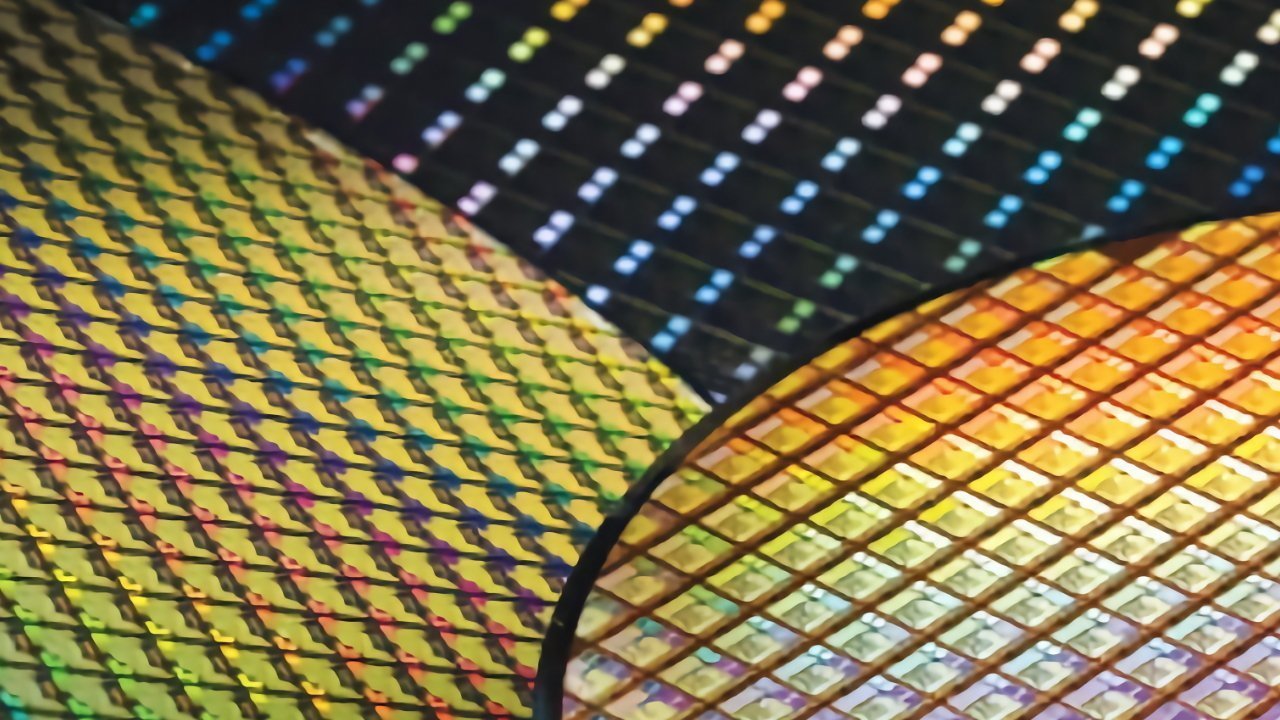

Dies on wafers - Image credit: TSMC

One of the problems with chip production is that manufacturers are usually locked into a few specific chip designs, due to the expense and difficulty of creating each one. However, using a new technique will potentially allow TSMC to provide Apple with far more flexibility than ever before.

According to analyst Ming-Chi Kuo on Tuesday, Eternal Materials has been named as an advanced packaging materials supplier to TSMC. Eternal will become the only supplier of the liquid molding compound (LMC) and molding underfill (MUF), used to encapsulate chips, for Apple's 2026 iPhone and Mac chip generations.

The order from Eternal effectively confirms a claim from October 2024 that TSMC will be using a new technique to make Apple's chips in a more flexible way.

Ming-Chi Kuo has a very good record when it comes to Apple-related claims. The accuracy of the supply chain checks are his strong suit, such as stories like this about supplier changes.

From InFO to WMCM

Chip packaging refers to a way to set up the chip's die, as well as encapsulating it. The process also prepares the chip to communicate with other components on a circuit board, such as the components of an iPhone.

InFO (Integrated Fan-Out), the current technique, is used because Apple's non-CPU components are integrated into the chip package. That is, memory is added to the chip package directly instead of being an external component, improving memory performance overall.

The technique works well because Apple is using a single die housing the CPU, GPU, and the Neural Engine, and limited memory configurations. WMCM (Wafer-level Multi-Chi Module) is a different packaging technique that is better suited for a wider number of configurations.

WMCM is capable of putting together multiple dies into a single package, one that is still small enough for Apple's purposes. By using WMCM, Apple can have separate dies for the CPU, the GPU, and the Neural Engine, Apple can better mix and match the combinations of each, increasing the number of different chip configurations it could produce.

This can be imagined by using one CPU, GPU, and Neural Engine for chips destined in a Pro-tier iPhone, but then switching the GPU for one with more cores for use as an M-series chip. Apple could also differentiate the chips between the A20 and A20 Pro further by adding more powerful dies to one package, and using different sets for the other, while still using the same CPU.

Rumor Score: Possible

Read on AppleInsider

Comments

that would give the processes running on each module full speed access between cores. Then pack the same modules in different configurations to make the whole M family use the connecting module as the platform hub that has all the single and device specific functions