commentzilla

About

- Username

- commentzilla

- Joined

- Visits

- 131

- Last Active

- Roles

- member

- Points

- 2,629

- Badges

- 2

- Posts

- 801

Reactions

-

Evidence of 'copy-acquire-kill' strategy could play role in big tech antitrust hearing

A much older concept, "Embrace, extend, and extinguish"

"Embrace, extend, and extinguish" (EEE),[1] also known as "embrace, extend, and exterminate",[2] is a phrase that the U.S. Department of Justice found[3] was used internally by Microsoft[4] to describe its strategy for entering product categories involving widely used standards, extending those standards with proprietary capabilities, and then using those differences in order to strongly disadvantage its competitors."

https://en.wikipedia.org/wiki/Embrace,_extend,_and_extinguish

-

Apple silicon Macs to support Thunderbolt despite shift to ARM

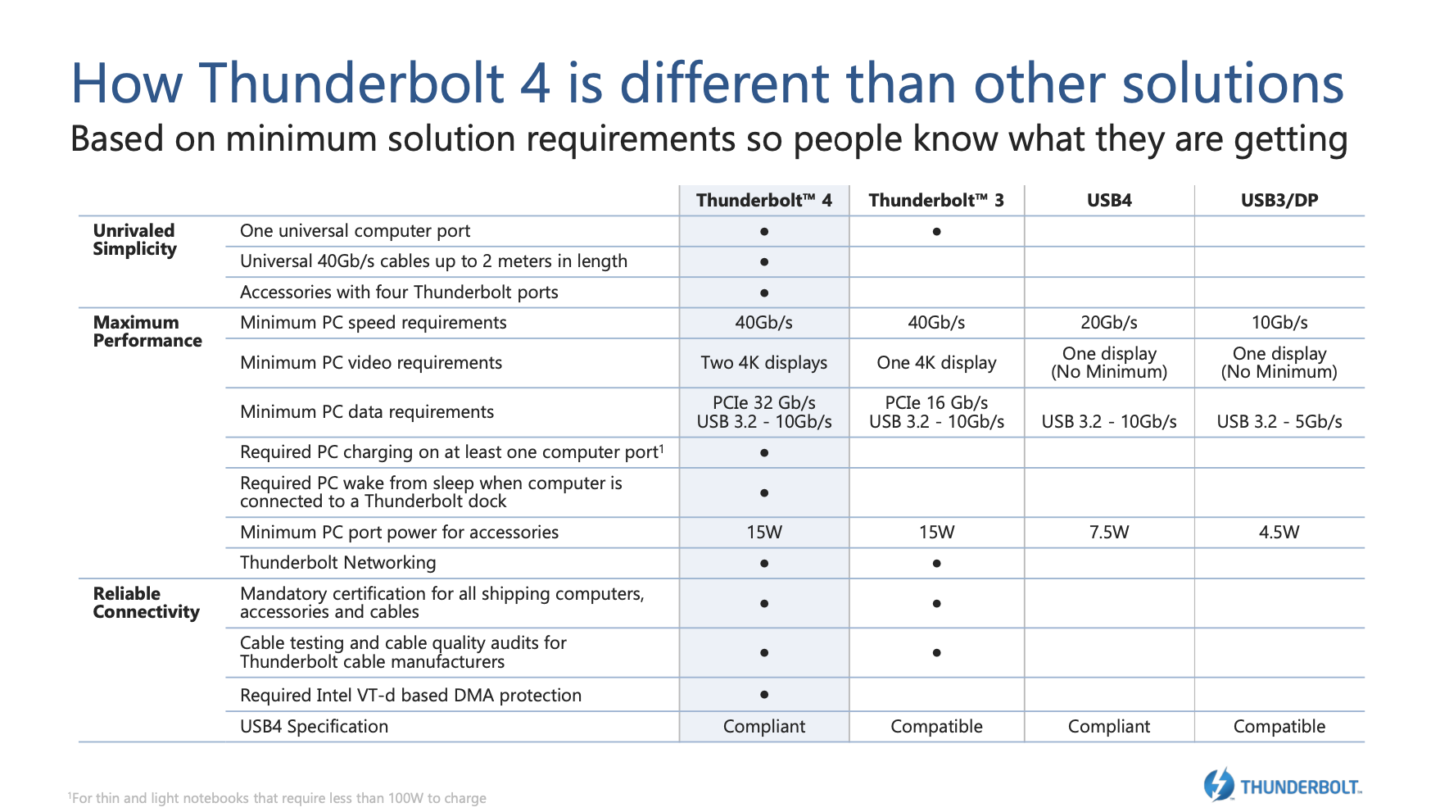

That's incorrect. TB4 bring new features along with USB4. One it mandates a certain level of support and strengthens some of the features.prismatics said:TB4 is kindof Fake.

It doesn’t bring any urgently needed speed bump and Apple supports everything TB4 supports with TB3 chips already.

Originally, TB4 was a fake news Intel released with Tiger Lake at CES2020 because they were caught with their pants down shortly after AMD released their wildly successful Renoir notebook processors and didn’t have anything new to show.

Ignore it and wait for TB5.- Double the minimum video and data requirements of Thunderbolt 3

- Video: Support for two 4K displays or one 8K display.

- Data: PCIe at 32 Gbps for storage speeds up to 3,000 MBps.

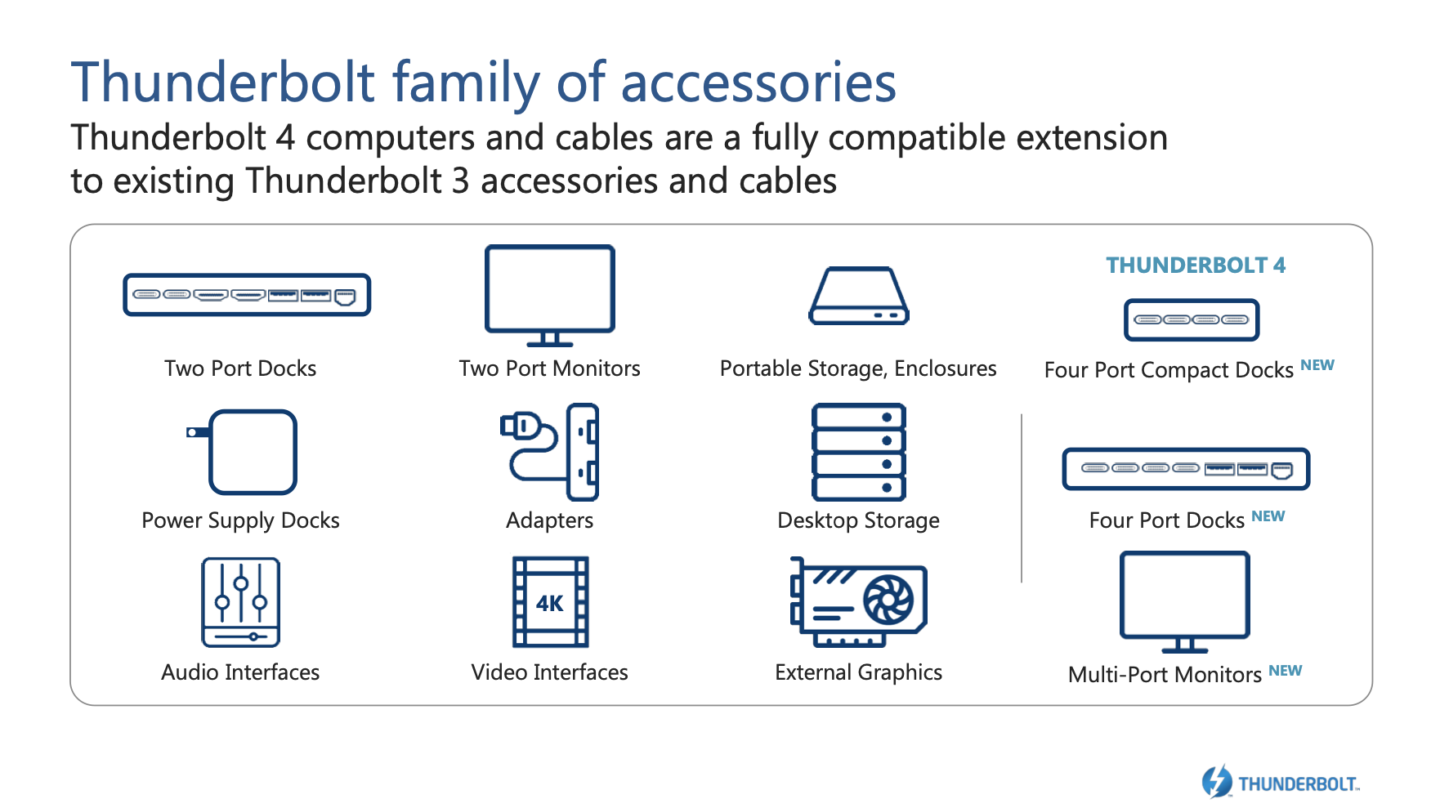

- Accessories with four Thunderbolt 4 ports

- Universal 40GB/s cables up to 2 meters in length

- Required PC charging on at least one computer port.

- Required PC wake from sleep when computer is connected to a Thunderbolt dock

- Required Intel VT-d-based direct memory access (DMA) protection

- USB4 specification compliant

- Double the minimum video and data requirements of Thunderbolt 3

-

LinkedIn blames bug for clipboard snooping discovered by iOS 14

-

Apple Silicon Mac mini dev kit looks like a desktop iPad Pro

I don't think there was a side by side demo because the A12Z isn't going to be the shipping chip. I'm betting on a beefier design meant to wow the crowd.mretondo said:Apple made it perfectly clear that ARM is slower than Intel. In fact they screamed it out load if you were listening. There wasn’t a single side by side demo of FCP X running on two Macs doing a long task like rendering. Intel takes 2 minutes while ARM takes 1.5 minutes. That’s all it would’ve taken to show how fast ARM is. The reason, ARM is slower!

That aside, my 2020 13" MBP 10th GEN i7 can't run Tomb Raider at 30 fps in 1080p. That told me everything I needed to know. Most everything they showed would choke my brand new MBP. While the graphics are impressive they'll need a beefier design to eliminate AMD/NIVIDA dGPUs.

-

Why the Mac's migration to Apple Silicon is bigger than ARM

So far Apple appears to be winning with RISC. The A-12 is already matches at the 10th Gen i7 Quad-Core in single, multi-core, and beating it hands down in GPU performance. One of the reasons Apple is moving on.anonconformist said:

Fast cache is heavier for power usage as well as space, and taking more space requires more time for the whole system to some degree, not to mention the more space a chip takes, the more expensive it is to make, as the higher number of defective chips you’ll have on any given die.commentzilla said:anonconformist said:rmusikantow said:

Yes. I just read that the new Japanese super computer, that is the fastest in the world is built using Arm chips.darthw said:Will it be possible, eventually, for Apple to make faster SoCs than the fastest most powerful intel Xenon chips?

can Apple eventually make their own SoCS to beat Intel Xeons? There are reasons that it could go either way:

ARM ISA is easier to decode is in its favor.

intel z86-64 ISA is more compact due to variable length instructions that reduce memory bandwidth required for a given number of of instructions that achieve the same thing.

I think there is zero chance Apple will stay with INTEL anything and they will have no issue out performing INTEL Xeons within the same power and thermal constraints.

INTEL chips bring a lot of baggage to include more complex instructions so I doubt they're more compact and while fixed length instructions may require more bandwidth....

"Fixed-length instructions are less complicated to handle than variable-length instructions for several reasons (not having to check whether an instruction straddles a cache line or virtual memory page boundary, for instance), and are therefore somewhat easier to optimize for speed."

Space matters, and if they can deal with the variable length instructions in less decoding logic space/power than the caches required, it’s a win. It’s not just about bandwidth to/from main memory, also internally, and size matters. Resistance and capacitance increase with the size, and that increases power while decreasing speed as well: it makes the most sense to use the least total hardware regardless of the complexity of decoding basic instructions into the micro-ops, of which there are far fewer micro-ops ever in-flight at any given time than CPU caches storing ISA machine code and its data.